# RAIO RA8803/8822

# Two Layers Text/Graphic LCD Controller Specification

Version 1.1

April 26, 2004

RAiO Technology Inc.

©Copyright RAiO Technology Inc. 2003, 2004

# 1. General Description

The RA8803/RA8822 is a Dot-Matrix LCD controller which support both text and graphics mode. It built-in two Display RAM for two layers display, and embedded a 512Kbyte character ROM that consists of Chinese, English and ASCII fonts. In text mode, the RA8803/8822 support Chinese BIG5 code or GB code. The system (MPU) does not need take a lot of time to show the Chinese font in graphics mode.

The RA8803/8822 support 8080/6800 like MPU interface, and also provide 4-Bit or 8-Bit data bus. For LCD driver interface, it support the most of LCD Driver in the world. The RA8803 support maximum LCD panel is 320x240 dots, and RA8822 is 240x160 dots. If use extension mode then the RA8803 support up to 640x240(320x480) dots Panel, and RA8822support up to 480x160(240x320) dots. The embedded 10-Bit ADC and Analog Switch provide the 4-wires Touch Panel interface. The 5-Bit DAC provides the contrast control of the LCD panel. The RA8803/8822 also provide an 8x8 Key-Scan interface that reduces the loading of MPU. Except for 16x16 Chinese font size, RA8803/8822 also provides a great choice of different font sizes, such as 32x32, 48x48, or even 64x64. The embedded 512Byte SRAM allows user build their own characters or symbols for convenience.

The RA8803/8822 is a high integration chip of LCD Controller. It reduce a lot of time for system develop, and save much cost for hardware system that due to it provides many features for related LCD display application.

#### 2. Feature

- Support Text and Graphics Mode

- Support 2-Layers Display(AND, OR, NOR, XOR), Built-in Two 9.6K/4.8Kbyte Display Data RAM

- Dual Page Support Maximum 320x240(RA8803) Or 240x160(RA8822) Dots Panel

- Extension Mode RA8803: 640x240(320x480)

RA8822: 480x160(240x320) Dots

- ◆ Support 4/8Bit of 6800/8080 MPU Interface

- Built-In 8x8 Key-Scan Circuit

- Support Horizontal and Vertical Scrolling

- Support 4/8Bit LCD Driver Interface

- ◆ Built-In 512KByte Font ROM,

- \_ RA8803/8822-T : 13,094 Traditional Chinese Fonts

- \_ RA8803/8822-S : 7,602 Simple Chinese Fonts

- ◆ Built-In 512Byte SRAM for Create Font

- Font Size Adjustable: 32x32, 48x48 or 64x64, and V/H Mixed Mode

- Support Full Size(16x16) and Half Size(8x16)

Mode

- ◆ Font ROM Readable

- ◆ Support Align Function

- ◆ Support 4 Gray Layer Display

- Support Bold Font and Line Distance Setting

- Built-In 10-Bit ADC for Touch Panel

- Built-In 5-Bit DAC for Contrast Control

- ◆ Clock: 32KHz X'tal or External Clock

- ◆ Power Supply: 2.4~5V

- ◆ Package: Die , PQFP/LQPF 100Pins

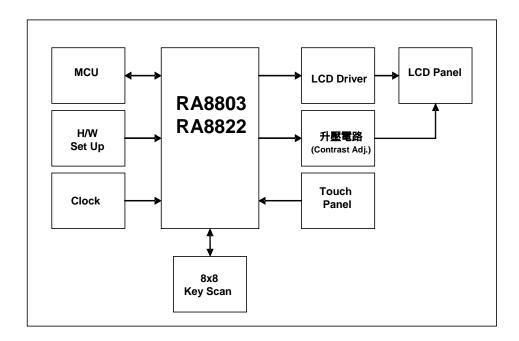

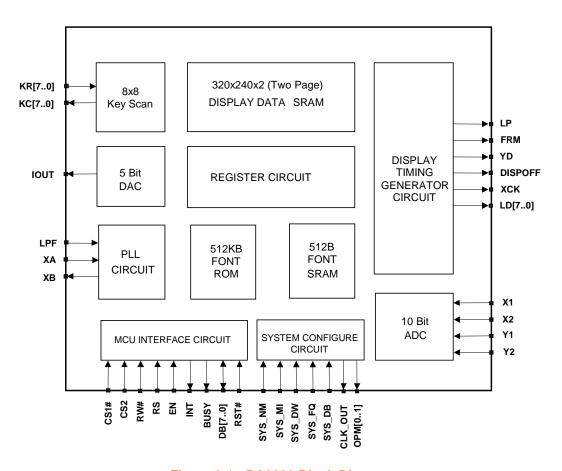

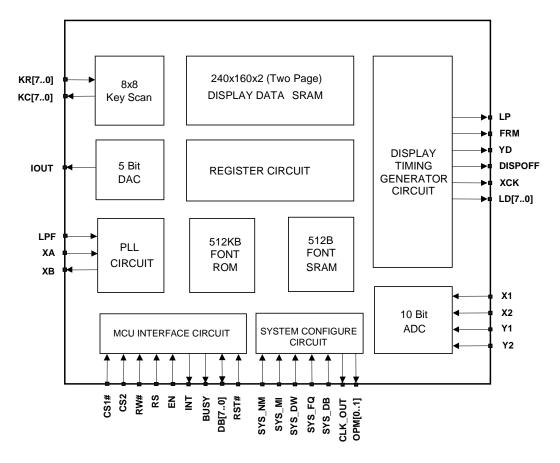

# 3. Block Diagram

Figure 3-1 is the internal block diagram of RA8803. The RA8803 consists of Display RAM, 512Kbyte Font ROM, Command Registers, Analog to Digital Converter(ADC), Digital to Analog Converter(DAC), Display Timing Generator(DTG) and Microprocessor interface. Figure 3-2 is the internal block diagram of RA8822. The major different of RA8803 and RA8822 is the Display RAM size.

Figure 3-1: RA8803 Block Diagram

Figure 3-2: RA8822 Block Diagram

# 4. Pin Definition

#### 4.1 MPU Interface

| Pin Name      | I/O | Description                                                                                                                                                                 |  |  |

|---------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DB[70]        | I/O | Data Bus These are data bus for data transfer between MPU and RA8803/8822. The high nibble DB[74] should be floating when 4-bit data bus mode is used.                      |  |  |

| EN<br>(RD#)   | I   | Enable/Read Enable When MPU I/F is 8080 series, this pin (RD#) is used as data read, active low. When MPU I/F is 6800 series, this pin (EN) is used as Enable, active high. |  |  |

| R/W#<br>(WR#) | I   | Write/Read-Write When MPU I/F is 8080 series, this pin (WR#) is used as data write, active low. When MPU I/F is 6800 series, this pin(R/W#) is used as data read/write      |  |  |

|      |   | control. Active high for read and active low for write.                      |  |  |

|------|---|------------------------------------------------------------------------------|--|--|

|      | I | Register/Memory Select                                                       |  |  |

| RS   |   | The MPU will access Register when RS is Low and access Data Memory           |  |  |

| K5   |   | when RS is High.                                                             |  |  |

|      |   | Usually connect to MPU address bus A0.                                       |  |  |

| CS1# |   | Chip Select                                                                  |  |  |

| CS2  | ' | The RA8803/8822 is active when CS1# is low and CS2 is high                   |  |  |

|      | 0 | Interrupt Signal                                                             |  |  |

| INT  |   | This is an interrupt output to indicate the status of RA8803/88822. It could |  |  |

|      |   | be setup active high or low.                                                 |  |  |

|      |   | Busy Signal                                                                  |  |  |

|      | 0 | This is a busy output to indicate the RA8803/88822 is in busy state. It      |  |  |

| BUSY |   | could be setup active high or low. If setup active high, the RA8803/8822     |  |  |

|      |   | can't be access when BUSY pin is high.                                       |  |  |

|      |   | It's should be connected to MPU I/O input. The MPU have to poll this pin     |  |  |

|      |   | before accessing RA8803/8822.                                                |  |  |

### 4.2 LCD Driver Interface

| Pin Name | I/O | Description                                                                 |  |  |

|----------|-----|-----------------------------------------------------------------------------|--|--|

| YD       | 0   | Start Signal of LCD Per Frame                                               |  |  |

| I D      |     | YD is the frame start signal.                                               |  |  |

|          | 0   | Control Signal of LCD AC Wave                                               |  |  |

| FRM      |     | This signal controlt the Level Shift of LCD driver. Normally inputs a frame |  |  |

|          |     | inversion signal.                                                           |  |  |

| LP       | 0   | LCD Common Latch                                                            |  |  |

| Lr       |     | This is a latch signal for LCD driver to latch the Common data.             |  |  |

| XCK      | 0   | LCD Clock                                                                   |  |  |

| ACK .    |     | This is a shift clock signal for LCD driver.                                |  |  |

| DISPOFF  | 0   | LCD Display OFF                                                             |  |  |

| DISPOPE  |     | This signal is used to control the LCD Display ON or OFF.                   |  |  |

|          | 0   | LCD Driver Data Bus                                                         |  |  |

| LD[70]   |     | When 8-bit LCD driver IC is used. LD[70] are connected to LCD driver        |  |  |

| LD[10]   |     | data bus. When 4-bit CPU is used, LD[30] are connected to LCD driver        |  |  |

|          |     | data bus, but LD[74] are non-connected.                                     |  |  |

#### 4.3 Clock Interface

| Pin Name | I/O | Description                                                                    |  |

|----------|-----|--------------------------------------------------------------------------------|--|

| LPF      | ,   | Low Pass Filter Input                                                          |  |

|          | '   | This is a low pass filter input. Please refer the circuit of application note. |  |

|    |   | X'tal Input                                                           |

|----|---|-----------------------------------------------------------------------|

| XA | I | In internal clock mode, this pin connects to external X'tal(32768Hz). |

|    |   | In external clock mode, this is an input of external clock.           |

| ХВ | 0 | X'tal Output                                                          |

|    |   | This pin connects to external X'tal(32768Hz).                         |

#### 4.4 Peripheral Interface

| Pin Name                              | I/O | Description                                                                |  |  |

|---------------------------------------|-----|----------------------------------------------------------------------------|--|--|

| RST#                                  | I   | Reset Signal                                                               |  |  |

| K51#                                  |     | This is a reset signal used to reset RA8803/8822. Active low.              |  |  |

| X1                                    | I   | Touch Panel Input                                                          |  |  |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |     | This is connecting to the left pin of 4-wire touch panel.                  |  |  |

| X2                                    | 1   | Touch Panel Input                                                          |  |  |

| ΛZ                                    | '   | This is connecting to the right pin of 4-wire touch panel.                 |  |  |

| Y1                                    | ı   | Touch Panel Input                                                          |  |  |

|                                       | '   | This is connecting to the top pin of 4-wire touch panel.                   |  |  |

| Y2                                    | ı   | Touch Panel Input                                                          |  |  |

| 12                                    | '   | This is connecting to the bottom pin of 4-wire touch panel.                |  |  |

| IOUT                                  | 0   | DAC Current Output                                                         |  |  |

| 1001                                  |     | DAC current source output used to contrast voltage control.                |  |  |

| KR[70]                                | I   | Key Pad Input                                                              |  |  |

| KK[70]                                |     | These pins are keypad inputs.                                              |  |  |

| KC[7.0]                               | 0   | Key Pad Output                                                             |  |  |

| KO[7.0]                               |     | These pins are keypad outputs.                                             |  |  |

| CLK_OUT                               | 0   | Clock Output                                                               |  |  |

| CLK_OOT                               |     | This is system clock output pin.                                           |  |  |

| SYS_NM                                | 1   | Test Pin                                                                   |  |  |

| 313_IVIVI                             | '   | This is a test pin. Normally it has to connect high.                       |  |  |

|                                       |     | System Clock Select                                                        |  |  |

|                                       |     | This pin is used to select clock source.                                   |  |  |

|                                       |     | Pull Low (0): X'tal/PLL Mode.                                              |  |  |

| SYS FQ                                | l , | Pull High(1): External Clock.                                              |  |  |

|                                       | '   | When SYS_FQ is Pull Low, then Internal oscillator and PLL are enable,      |  |  |

|                                       |     | only one external 32Khz X'tal need.                                        |  |  |

|                                       |     | When SYS_FQ is Pull High, then the system clock is from external pin "XA". |  |  |

|                                       | I   | LCD Driver Data Bus Select                                                 |  |  |

| SYS_DW                                |     | This pin is used to select data bus of LCD driver is 8-Bit or 4-Bit:       |  |  |

| J 13_DVV                              |     | Pull Low(0): 4-Bit                                                         |  |  |

|                                       |     | Pull High(1): 8-Bit                                                        |  |  |

|        | ī | T                                                                                   |           |                                                    |  |  |

|--------|---|-------------------------------------------------------------------------------------|-----------|----------------------------------------------------|--|--|

|        |   | When SYS_DW is Pull Low, then the LCD driver data bus Is 4-Bit.                     |           |                                                    |  |  |

|        |   | When SYS_DW is Pull High, then the LCD driver data bus is 8-Bit.                    |           |                                                    |  |  |

|        |   | MPU Type Select                                                                     |           |                                                    |  |  |

|        |   | This pin is used to select MPU type:                                                |           |                                                    |  |  |

|        |   | Pull Low(0): I8080 Series                                                           |           |                                                    |  |  |

| SYS_MI |   | Pull High(1): M6800 Series                                                          |           |                                                    |  |  |

| 0.10   |   | When SYS                                                                            | S_MI is P | ull Low, then the MPU Interface of RA8803/8822 is  |  |  |

|        |   | suppported                                                                          |           |                                                    |  |  |

|        |   |                                                                                     |           | ull High, then the MPU Interface of RA8803/8822 is |  |  |

|        |   | supported M6800.                                                                    |           |                                                    |  |  |

|        |   | MPU Data Bus Select                                                                 |           |                                                    |  |  |

|        |   | This pin is used to select data bus of MPU is 4-Bitor 8-Bit:                        |           |                                                    |  |  |

|        |   | Pull Low(0): 4-Bit                                                                  |           |                                                    |  |  |

| SYS DB | ı | Pull High(1): 8-Bit                                                                 |           |                                                    |  |  |

| _      |   | When SYS_DB is Pull Low, then the MPU Interface of RA8803/8822 is                   |           |                                                    |  |  |

|        |   | supported 4-Bit.                                                                    |           |                                                    |  |  |

|        |   | When SYS_DB is Pull High, then the MPU Interface of RA8803/8822 is                  |           |                                                    |  |  |

|        |   | supported 4-Bit.                                                                    |           |                                                    |  |  |

|        | 0 | Operation Status of Current Command                                                 |           |                                                    |  |  |

|        |   | These two pins are the feedback from RA8803/8822 while MPU release a                |           |                                                    |  |  |

|        |   | Read or Write command to RA8803/8822. The MPU could know the status of RA8803/8822. |           |                                                    |  |  |

|        |   |                                                                                     | 1         |                                                    |  |  |

| OPM0   |   | ОРМ0                                                                                | OPM1      | State                                              |  |  |

| OPM1   |   | 1                                                                                   | 0         | MPU is reading data from RA8803/8822.              |  |  |

| J      |   | 1                                                                                   | 1         | MPU is writing data to RA8803/8822.                |  |  |

|        |   | 0                                                                                   | Х         | RA8803/8822 did not receive command or read        |  |  |

|        |   |                                                                                     |           | a valid commend.                                   |  |  |

|        |   | These two pins should be floating for not use.                                      |           |                                                    |  |  |

#### 4.5 Power

| Pin Name | I/O | Description                                          |  |  |

|----------|-----|------------------------------------------------------|--|--|

| VDD      | ı   | Digital Power                                        |  |  |

| VDDP     | ı   | I/O Power                                            |  |  |

| AVDD     | ı   | Analog Power                                         |  |  |

| GND      |     | Ground                                               |  |  |

| GNDP     | '   | Ground                                               |  |  |

| AGND     | I   | Analog Ground                                        |  |  |

| TEST     | I   | Test Pin                                             |  |  |

|          |     | This pin is for test only and don't need to connect. |  |  |

# 5. System Block Diagram